### MODULE-1 ARM 32-BIT MIC ROCONTROLLER.

B.S. Balaji Asst. Prof BGSIT.

Introduction ARM CORTEX M3 - PROCESSOR.

- The requirement for higher performance microcontrollers has been driven globally by the industry's changing needs;

for example, micro controllers are required to handle more work

without increasing a product's frequency or power.

- Microcontrollers are becoming increasingly connected whether by Universal Serial Bus (USB), Ethernet, or wireless radio, and

hence, the processing needed to support these communication channels and advanced peripherals are growing.

-> General application complexity is on the rise due to more sophisticated wer interface, multimedia requirements, system speed, and convergence of functionalities.

> The ARM Cortex-M3, processor, the first of the Cortex generation of processors released by ARM (Advanced RISC (Reduced Instruction Set

Computing) Machines) in 2006.

It provides excellent performance at low gate count and comes with many new features previously available only in high end processors.

-) It addresses the requirements of 32 bit embedded processor like-

(i) Greater performance efficiency - It allows more work to be done without increasing the frequency or power requirements.

(ii) Low power consumption - It enables longer battery life, especially critical in portable products like wireless networking applications.

(iii) Enhanced determinism - It guarantees that critical tasks and interrupts

are serviced as quickly as possible and in a known number of cycles.

(iv) Improved code density - It ensures that code fits in even the smallest

memory footprints. (v) Ease of use - It provides easier programmability and debugging for the growing number of 8-bit and 16-bit users migrating to 32 bits.

- (vi) Lower cost solutions It reduces 32-bit based system close to those of legacy 8-bit and 16-bit devices and enabling low-end, 32 bit micro controllers.

- (vii) Wide choice of development tools The availability of clow-cost or tree compilers to full-featured development suites from many development tool vendors.

- Cortex M3 processor builds on the success of the ARM7 processor to deliver devices that are significantly easier to program and debug and yet deliver a higher processing capability.

- It can be easily programmed using the Clanguage and are based on a well-established architecture, application code can be ported and reused easily, reducing development time and testing costs.

- It introduces a no. of features and technologies that meet the specific requirements of the micro controller applications such as

- \* non maskable interrupts for critical tasks,

- \* highly deterministic nested vector interrupts,

- \* atomic bit manipulation, and

BALL OF CHE BY TENES

\* an optional Memory Protection Unit (MPU).

# Background of ARM and ARM Architecture

- ARM was formed in 1990 as Advanced RISC Machines Ltd., a joint venture of Apple Computer, Acorn Computer Group, and

- → In 1991, ARM introduced the ARM6 procusor family, and

- VLSI became the initial licensee.

- Additional companies, including Texas instruments, NEC, Sharp, and ST Microelectronics, licensed the ARM processor designs.

- Applications of ARM processors into mobile phones, computer hard disks, personal digital assistants (PDAs), home entertainment systems etc.

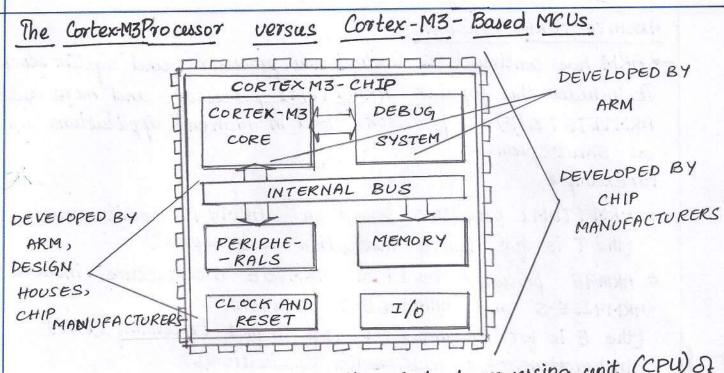

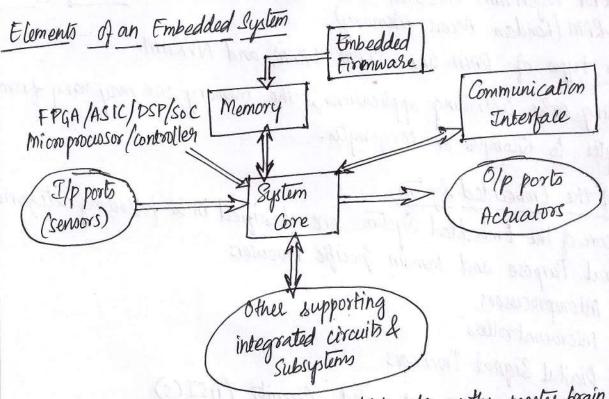

- The Cortex-M3 processor is the Central processing unit (CPU) of a microcontroller chip. Inaddition, a no. of other components are required for the whole Cortex-M3 processor-based microcontroller.

-> After chip manufacturers license the Cortex-M3 processor, they can put the Cortex-M3 processor in their silicon designs, adding memory, peripherals, input (output (I/O), and other features.

-> Cortex-M3 procussor-based chips from different manufacturers will have different memory sizes, types, peripherals, and features.

> ARM does not manufacture processors or sell the chips directly. -> ARM licenses the processor designs to business partners, including

a majority of the world's leading semiconductor companies.

> Based on the ARM low-cost and power efficient processor designs, these portners (such as NXP (Philips), Texas Instruments, Atmel, OKI etc.) create their processors, microcontrollers, and system on chips solutions. It called as intellectual property (IP) licensing.

-> ARM also licenses systems-level IP and various software IPs.

ARM has developed a strong base of development tools, hardware and software products to enable partners to develop their own products.

#### ARCHITECTURE VERSIONS

-> ARM has continued to develop new processors and system blocks. It includes the popular ARMTTDMI processor and more recently ARM1176TZ (F)-S processor used in high end applications such as smart phones. For example

\* ARMITOMI processor based on ARMV4T architecture

(the T is for Thumb instruction mode support).

\* ARM9E processor based on ARMV5E architecture includes ARM926E-S and ARM946E-S procusors. (the E is for "Enhanced" Digital Signal Processing (DSP) instructions for multimedia applications).

\* ARMIL processor based on ARMV6 architecture includes new features memory system features and Single Instruction-Multiple

Data (SIMD) instructions.

ARMV6 architecture also includes the ARM1136J(F)-S, the ARM1156T2(F)-5 and the ARM1176JZ(F)-3.

The architecture is divided into three profiles -

1) A-Profile (ARMV7-A): It is det designed for high-performance open \* Application processors which are designed to handle complex applications such as high-end embedded operating systems (OSS) e.g., Symbian, Linux and Windows embedded.

\* These processors requires the highest processing power, virtual memory

system support with memory management units (MMUs).

2) R-Profile (ARMUT-R): It is designed for high end embedded systems in which real-time performance is needed.

\* Real-Time, high processors performance processors targeted primarily at the higher end real time market applications like high-end breaking systems and hard drive controllers with high processing power and high reliability.

3) 19-Profile (ARMV7-R): It is designed for deeply embedded micro-

-controller type systems.

\* It targets low-cost applications with processing efficiency important and cost, power consumptions, low interrupt latency and ease of use are critical as well as industrial control applications, including real-time control systems.

THE THUMB - 2 TECHNOLOGY

The Thumb-2 technology extended the Thumb Instruction Set

Architecture (ISA) into a highly efficient and powerful instruction set.

The delivers significant benefits in terms of ease of use, code size, and performance.

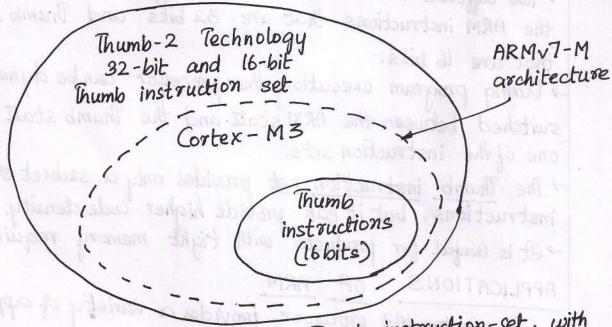

→ The Relationship between the Thumb Instruction Set in Thumb-2 Technology and the Traditional Thumb.

It is a superset of the previous 16-bit Thumb instruction-set, with additional 16-bit instructions alongside 32-bit instructions.

In 2003, ARM announced the Thumb-2 instruction set, which is a new instruction super set of Thumb instructions that contains both 16 bit and 32 bit instructions.

It allows more complex operations to be carried out in the Thumb state, thus allowing higher efficiency by reducing the number of states switching between ARM state and Thumb state.

It focuses on small memory system devices such as microcontrollers and reducing the size of the processor.

-> The Cortex-M3 supports only the Thumb-2 (and Traditional Thumb) instruction set; especially uses Thumb-2 instruction set for all operations instead of using ARM instructions for some operations as in traditional ARM processors.

-> With support for both 16 bit and 32 bit instructions in the Thumb-2 instruction set, there is no need to switch the processor between Thumb state (16-bit) instructions) and ARM state

(32-bit instructions).

- The Cortex M3 procusor also supports unaligned data accessess, a feature previously available only in high-end processors.

# Instruction Set development

- Two different instruction sets are supported on the ARM processor: the ARM instructions that are 32 bits and humb instructions that are 16 bits.

- During program execution, the processor can be dynamically switched between the ARM state and the Thumb state to use either

one of the instruction sets.

The Thumb instruction set provides only a seebset of ARM instructions, but it can provide higher code density.

It is useful for products with tight memory requirements.

# APPLICATIONS OF ARM

The Cortex-M3 processor provides a variety of applications-1) the Low-cost microcontrollers- The cortex-M3 processor is well

suited for microcontrollers, which are commonly used in consumer products, from toys to electrical appliances. - Its lower power, high performance, and ease of use advantages enable embedded developers to migrale to 32-bit systems and

dwelop products with the ARM architecture.

2) Automotive - The Cortex-M3 processor has very high-performance efficiency and low latency, allowing it to be used in real time systems. Hence it is ideal application is for Cortex-M3 processor in automotive industry.

- It supports up to 240 external vectored interrupts, with a built-in interrupt controller with nested interrupt supports and an optional MPU which makes easily available as highly integrated and cost-sensitive automotive applications.

3) Data Communications -

- The processor's low power and high efficiency, coupled with instructions in Thumb-2 for bit-field manipulation, make the Cortex-M3 ideal for many communications applications, such as Bluetooth and ZigBee.

4) Industrial Control-

- In Industrial control applications applications, simplicity, fast

response, and reliability are key factors.

- The Cortex-M3 processor's interrupt feature, low interrupt latency, and enhanced foult-handling teatures (make it a strong candidate in this area).

5) Consumer products -

- In many consumer products products, a high performance

micro processor is used.

→ The Cortex-M3 processor, is a small processor, is highly efficient and low in power and supports an MPU enabling complex software to execute while providing robust memory protection.

# ARCHITECTURE OF ARM CORTEX -M3

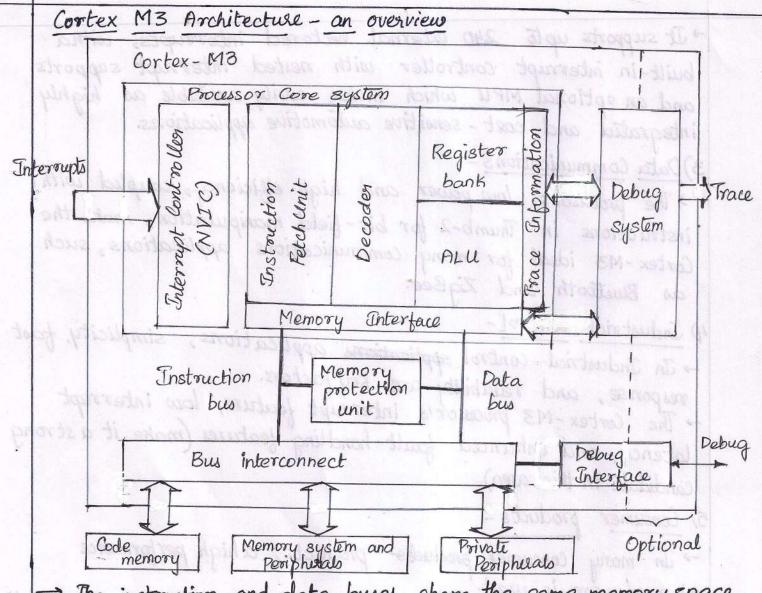

-> Arm Cortex-M3 is a 32 bit microprocessor. It has a 32-bit datapath, a 32-bit register bank, and 32-bit memory interfaces.

- It has a Harvard architecture which means a separate instruction bus and data bus. It allows instructions and data accesses to take place at the same time.

- As a result, the processor performance increases because data

accesses do not affect the instruction pipeline.

- It allows multiple bus interfaces in Cortex-M3 with optimized usage and ability to be used 67 simultaneously.

The instruction and data buses share the same memory space (a unified memory system).

for complex applications, which requires more memory system features, where the Cortex-M3 processor has an optional if its required Memory Protection Unit (MMPU) and external cache is can be used.

→ It supports both little endian and big endian memory systems.

It includes a no. of fixed internal debugging components. These components provide debugging operation supports and features such as breakpoints and watchpoints.

In addition, optional components provide debugging features, such as instruction trace, and various types of debugging interfaces.

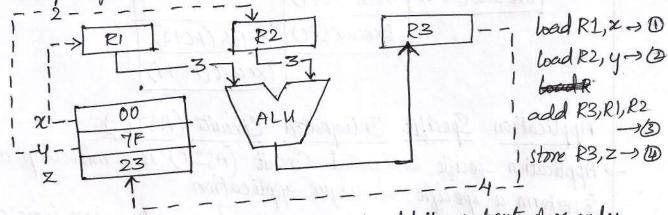

#### VARIOUS UNITS IN THE PRCHITECTURE-- architecture bes includes various The Cortex-M3 processor units like -1) Registers 2) Operation Modes 3) Nested Vectored Interrupt Controller (NVIC). 4) Memory Map 5) Bus Interface Memory Protection Unit. Instruction Set 7) 8) Interrupts and Exceptions 9) Debugging support. RO-R12- are 32 bit The Cortex-M3 procusor Ro has registers Ro through RIS, R15, 1) Registers -R13 (the stack pointer) is banked, with only one copy of the R13 visible at a time, R14 - link register and R15 is Program Functions (and Banked registers) Counter. Name General-Purpose Register General-Purpose Register Register RI General Purpose Low registers General Purpose Régister General Purpose Register R3 General Purpose Régister R4 Register R5 General Purpose General Purpose Register R6 General Purpose Register RT High registers Register R8 General Purpose General Propose Register R9 General Ropose Register RIO RII General Purpose Register. Main Stack Pointer (MSP), Process Stack Pointer (PSA) RIZ RI3(PSP) RI3 (MSP) Link Register (RR) Program Counter (PC) RIS Registers in the Cortex-M3

RO-RIZ General Purpose Registers

These are 32 bit General purpose registers for data operations. Some 16-bit instructions can only access a subset of these registers (now registers, RO-RT) and 32-bit registers instructions can anty access (RO-R12).

R13 - Stack Pointers

The Cortex M3 contains two stack pointers (R13). They are banked so that only one is visible at a time.

1) Main Stack pointer (MSP) .- The default stack pointer, used by the operating system (05) kernel and exception handless.

2) Process Stack pointer (PSP) - Used by user application code.

R14 - Link Register

when a subroutine is called, the return address is stored in the link register.

R R15- The Program Counter

The program counter is the current program address. This register can be written to control the programflow.

Special Registers - Cortex M3 procusor also has a no. of special registers. They are as follows - 1) Program Status registers (PSRs)

2) Interrupt Mask registers Special Registers in Cortex-M3 (PRIMASK, FAULTMASK, and BASEPRI)

3) Control register (CONTROL) XPSR Program Status registers

, Special PRIMASK Interrupt mask Registers. FAULTMASK register

BASEPRI REGISTERS AND THEIR FUNCTIONS Controlorgister

Provide arithmetic & logic processing flags (zeroflags assayflag), execution status and current executing interrupt number.

Disable all interrupts except the nonmaskable interrupt (NMI) and Register xPSR PRIMASK all interrupts except the NMI hard fault

Disable all interrupts of specific priority level or lower priority level FAULTMASK poivileged status and stack pointer selection BASEPRI Define CONTROL

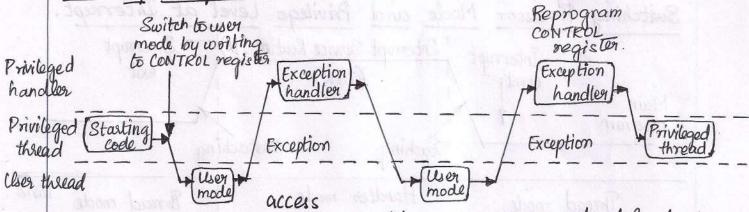

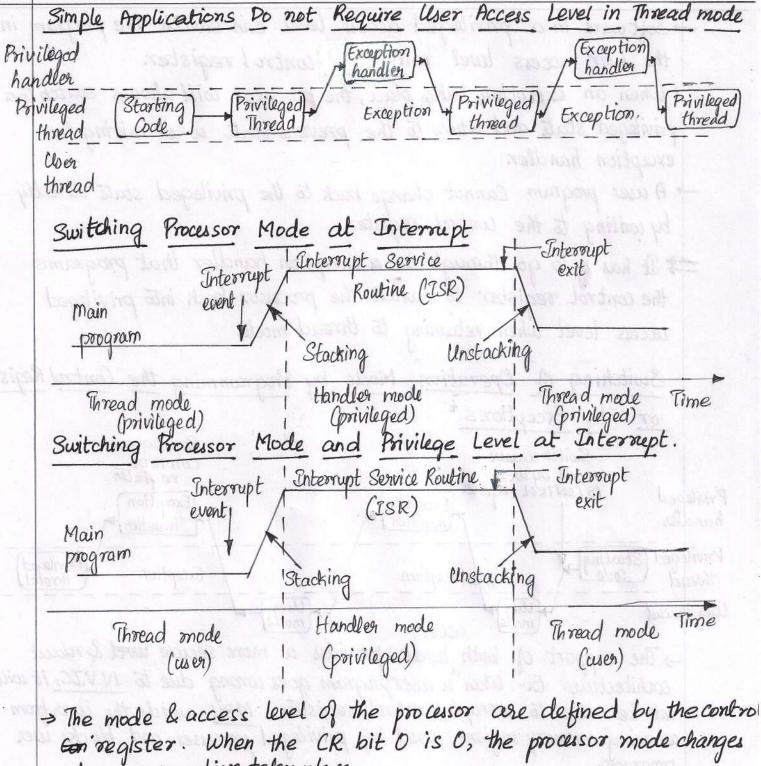

These registers have special functions and can be accessed only by special instruction instructions. 2) Operation modes - The Cortex-M3 processor has two modes and two privelege levels. → The operation modes (thread mode and handler mode) determine whether the processor is running a normal program or ounning an exception handles like an interrupt handles or system exception handler. Privileged When running an exception Handler mode handler When not ounning an exception Thread mode Thread mode handler (e.g. main program) Operation modes and Privilege levels in Costex M3. -> The privilege levels (privileged level and user level) provide a mechanism for safeguard memory accesses to critical regions as well as providing a basic security model. -> Software in the privileged access level can switch the program into the user access level using the control register. - When an exception takes place, the procusor will always switch back to the privileged state and return to the previous state when exiting the exception handler. Allowed Operation mode Transitions. Exception Privileged Start (neset) Exception Exception. Exception Privileged threag Clear thread

- Auser program cannot change back to the privileged state by -It has to go through an exception handler that programs the control writing to the control register. register to switch the processor back into privileged access level when returning

Program of

3) Built-in NESTED VECTORED INTERRUPT CONTROLLER.

-> Cortex-M3 procusor includes an interrupt controller called the Nested Vectored Interrupt Controller (NVIC).

- It provides a no. of features - 1) Nested interrupt support,

2) Vectored interrupt support

3) Dynamic priority changes support

4) Reduction of interrupt latency 5) Interrupt masking.

i) Nested Interrupt Support - The NVIC provides mested interrupt support. All the external interrupts and most of the system exceptions can be programmed to different priority levels.

2) vectored interrupt support- When an interrupt is accepted, the starting address of the interrupt service routine (ISR) is located from a vector table in memory.

3) Dynamic Priority changes support - Priority levels of Interrupts can be changed by software during our time.

4) Reduction of interrupt latency - It includes number of advanced features to lower the interrupt latency like automatic saving and restoring some register contents, reducing delay in switching from one ISR to another and handling of late arrival of interrupts.

5) Interrupt masking - Interrupts and system exceptions can be masked based on their priority level or masked completely using the interrupt masking registers BASEPRI, PRIMASK and

FAULT MASK.

They can be used to ensure that time-critical tasks can be finished on time without being interrupted.

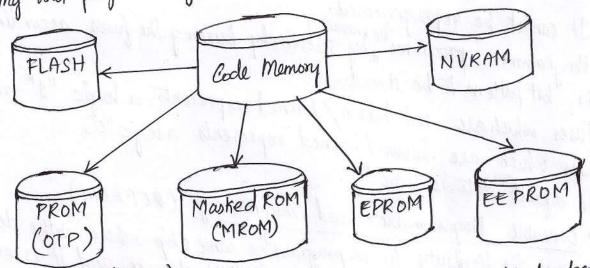

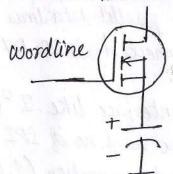

4) Memory Map

->Cortex M3 has a predefined memory map. It allows the built-in peripherals, such as interrupt controller and debug components to be accessed by simple memory access instructions.

- The predefined memory map also allows the processor to be highly optimized for speed and ease of integration in system-on-a-chip

(Soc) designs.

Thomas area 212

instruction Se

ions to be cue a

ves head (inter

Attions of ( for

ght nued labe

Overall, the 4GB memory space can be divided in to ranges as shown in figure.

The Cortex-M3 Memory Map

| 0x FFFFFFFF<br>0x 6000 0000              | System Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Private peripherals including build-in interrupt controller (NVIC), MPU control registers, and debug components.  Main used as external peripherals  Mainly used as External memory |  |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OXDFFFFFF                                | External device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                     |  |

| 0×9666000000                             | External RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                     |  |

| 0×5FFFFFFF<br>0×40000000                 | Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Mainly used as Peripherals                                                                                                                                                          |  |

| 0×3FFF FFFF<br>0×20000000<br>0×1FFF FFFF | SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Mainly used as static RAM                                                                                                                                                           |  |

| 0x00000000 L                             | CODE AND THE STATE OF THE STATE | Mainly used for program code. Also provides exception vector table after power up.                                                                                                  |  |

Cortex-M3 processor has many bus interfaces which allows to carry instruction fetches and data accesses at the same time. The BUS Interface

1) Code memory buses 2) System bus

3) Private peripheral bus.

- The Code memory region access is carried out on the code memory buses, which physically consist of two buses -I-code and D-code.

These are optimized for instruction fetches for best instruction

execution speed.

- The system bus is used to access memory and peripherals. It provides access to the Static SRAM, peripheral, External RAM, external devices, and part of the system-level memory

-> The private peripheral bus provides access to a part of the system level memory dedicated to private peripherals, such as

debugging components.

6) The MPU (Memory Protection Unit).

-> Cortex-M3 processor has an optional MPU. It allows access rules to be set up for privileged access and user program access.

7) THE INSTRUCTION SET

-> Cortex - M3 processor supports the Thumb-2 instruction set. It allows 32-bit instructions and lb-bit instructions to be used together for high code density and high efficiency.

-> It is flexible and powerful yet easy to use.

-> To get the best of both instruction set, There is a overhead (interms of both execution time and instruction space (as in figure) to switch between the states, and ARM and THUMB codes might need to be

compiled separately in different files. -> It increases the complexity and reducing maximum efficiency of core

Timing critical code ARM state (eg BXLR) (32-bit instructions) Overhead.

Branch with Main program Thumb state in Thumb state change (16 bit (eg BLX) instructions)

Main program in thumb state

> Pime

4) Time

8) Interrupts and Exceptions

- Cortex 143 processor implements a new exception model, enabling very efficient exception handling.

- It has a no-of system exceptions plus a no-of external Interrupt Request (IRQs) (external interrupt inputs).

-> There is no fast interrupt (FIG).

-> It supports nested interrupts (a higher-priority interrupt can override or preempt a lower-priority interrupt handles). behaves just like FIQ.

9) Low power Consumption

suitable for various low-power The Cortex-M3 processor is applications:

-> The Cortex-M3 processor is suitable for low power designs because of the low gate count. → It has power-saving mode support (SLEEPING and SLEEPDEEP).

→ The processor can enter sleep mode using WFI or WFE

-> The duign has separated clocks for essential blocks, so docking circuits for most parts of the processor can be stopped during sleep.

-> The fully static, synchronous, synthesizable design makes the processor easy to be manufactured using any low power or standard semiconductor process technology.

w) Debug supports

The Cortex M3 processor includes de comprehensive debug features (to help software developers design their products) -

-> Supports JTAG or Serial - wire debug interfaces

→ Based on the Coresight debugging solution, processor status or memory contents can be accessed even when the core is running.

-> Built-in support for six break points and four watchpoints.

-> Optional ETM for instruction trace and data trace using DWT.

- New debugging features, including fault status registers, new fault exceptions, and Flash Patch operations, making make debugging much easier.

-> ITM provides an easy-to-use method to output debug

The Contex - M3 processor is suitable for verifour low-power

- It has power- saving mede support (SLEEPING and SLEEPDEED)

information from test code.

-> PC samples and counters inside the DWT provide codeprofiling information.

- The Cortex-KIB processor, is suitable for low power designs

- The design has separated decisa for essential blocks, so

- The fully static, synchron u. synthesizable design make

the processor easy to be manufactured using any low power

The Cortex M3 processor includes the comprehensive debug

features (to help software developers during their products)

- Bused on the Consists debugging solution, processor statem

or memory centent can be accessed even when the core is

became of the low quie count.

stopped during sleep.

#### GENERAL PURPOSE REGISTERS

-> Cortex-M3 processor has registers Ro through R15 and a no-of special

registeus.

depault SP. Iti.

on handlers, and

by the base-level

909 bits 11209

tor example as FIH or LR)

h lash metruction

- Ro through R12 are general purpose, but some of 16 bit Thumb instructions Canonly access Ro through R7 (low registers), where as 32 bit Thumb-2 instructions can access all these registers.

- Special registers have predefined functions and can only be accessed by

Special registers access instructions.

Kegistes in the Cortex-M3

| e  | Cortex-140.   | Laster and a last settle last                               |

|----|---------------|-------------------------------------------------------------|

| _  | Name          | Functions (and banked registers)  General Purpose Registers |

|    | RO            | J General Purpose Register                                  |

| +  | RI            | Coneral Purpose Registry                                    |

|    | N 21 R2 - 916 | General Purpose Régister 1040                               |

|    | R3            | General Purpose Register 7                                  |

|    | R4            | 1 General                                                   |

|    | R5            | 1 General Respose Register                                  |

|    | R6            | 1 Ganoral Ruspose Register                                  |

| 31 | R7            | The seal primore keysees                                    |

|    | R8 1311 13    | General Purpose neglicities                                 |

| Ì  | R9            | (ioneral ruspase in 1) tous                                 |

|    | RID           | General Purpose Register registers                          |

|    | RII           | 1 General Purpose Regis                                     |

| 3  | F12           | General Purpose Register                                    |

| I  | RI3 (MSP)     | DIZ (PEP) Main Stack Police (MSP)                           |

| I  | RI4           | Link Register (LR) Proces Stack Pointer (131)               |

|    | RI5           | Danson (DUNIO(PC)                                           |

| 1  | ×PSR          |                                                             |

| F  | PRIMASK       | Program status Registers (1314) Special Special registers.  |

| F  | FAULT MASK    | Interrupt mask registers registers                          |

| F  | BASE PRI      | delication of Lucidania and the second                      |

|    | CONTROL       | Control registes                                            |

| -  |               |                                                             |

General Purpose Registers RO through R7.

-> They are all 32 bits; the reset value is unpredictable.

These are also called as low registers. They can be accessed by all 16 bit Thumb instructions and all 32-bit Thumb-2 instructions.

General Purpose Registers R8 through R12

These are also called as High registers. They are accessible by all thumbs? instructions but not by all 16-bit instructions.

- These registers are all 32 bits; the reset value is unpredictable.

Stack Pointer R13

→ R13 is the stack pointer. There are two SPs in Cortex M3 Processor.

→ Its duality allows two separate stack memories to be set up.

→ The use of Special instructions allows the selection of current SP. and other one is in accessible through move to special register from general purpose register (MSR) and move special register to general-purpose register (MRS).

1) Main Stack Pointer or SP-main - It is the default SP. It is used by the operating system (os) Kernel, exception handlers, and

all application codes that require privileged access.

2) Process Stack Pointer or SP-process-It is used by the base-level application code (when not running an exception handless).

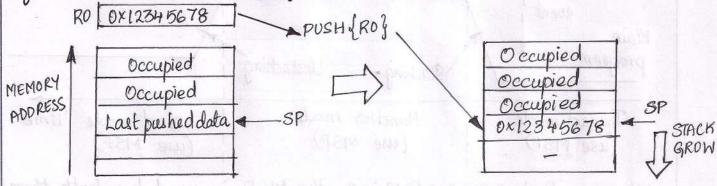

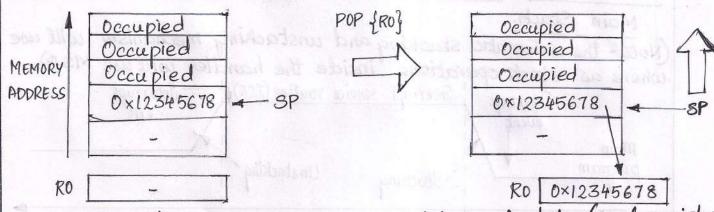

-> The instructions for accessing stack memory are PUSH and POP.

example -

PUSH [RO]; R13 = R13 - 4, then memory [R13] = RO POP [RO]; RO = Memory [RI3], then RI3 = RI3 + 4

-> The Cortex-M3 uses a full-descending stack arrangement.

Link Register R14

-> RH is the link negister (LR). It is used to store the neturn program Counter (PC) when a subroutine or function is called for example main: Main program (In assembly language, it can be used as R14 or LR)

BL function 1; Call function 1 using Branch with link instruction; PC = function 1 and

I LR = the next instruction in main

function 1; Program code for function 1

Krogram Counter R15 It is the Program Country (PC) and in assembles code as R15 or PC. > The value in PC is different than the location of executing instruction, normally by 4. ex- 0×1000: MOV RO, PC; RO = 0×1004 (18)

#### SPECIAL REGISTERS

The special registers in the Cortex-M3 procusor includes the

1) Program Status Registers (PSRs)

2) Interrupt Mask Registers (PRIMASK, FAULT MASK, and BASEPRI).

3) Control Register.

-> Special registers can only be accessed via MSR and MRS instructions; they do not have memory addresses:

MRS (reg), (special-reg); Read special register MSR (special-reg), (reg); write to special register.

Program Status Register

The PSRs are subdivided into three status registers:

- AU3 can be accessed together or separately using the special register access instructions MSR and MRS.

→ When they are accessed as a collective term, the name xPSR is used.

Combined Program Status Register (XPSR) in the Cortex-M3. 31 30 29 28 27 26:25 24 23:20 19:16 15:10 9 8 ICY/IT V Q ICI/IT T XPSR Exception number

Bit fields in Cootex-M3 Program Status negisters. Description Bit Description Sticky saturation flag ICI/IT Interrupt-Continuable Instruction (ICI) Negative bits/IF-THEN instruction status bit. Zeto Thumb state, always 1; trying to clear this bit will cause exception (fault) Carry/Borrow Overflow exception Indicates which exception the processor is

A whereas APSR You can read using the instruction. can also be changed using the MSR instruction, but EPSR and IPSR TO, APSR; Read flag state into RO are readonly. For example -MRS TO, IPSR; Read Exception/Interrupt state MRS

70, EPSR; Read Execution state MRS APSR, TO; Write flag state. MSR

In ARM assembler, when accessing XPSR (all 3 PSRs as one), the symbol ro, PSR; Read the combined Programstatus word PSR is wed: MRS PSR, 70; write the combined Program state word.

2 Interrupt Mask registers consists of PRIMASK, FAULTMASK, and BASEPRI registers which are used to disable exceptions.

→ The PRIMASK and BASEPRI registers are useful to temporarily disabling interrupts in timing - critical tasks.

The FAULT MASK gives the OS kernel time to deal with fault conditions and one used to temporarily disable fault handling when a task crashed. when a task crashed.

→ In assembly language, the MSR and MRS instructions are used. For example:

TO, BASEPRI; Read BASEPRI register into RO MRS

ro, PRIMASK; Read PRIMASK register into Ro MRS

TO, FAULTMASK; Read FAULTMASK register into RO MRS

BASEPRI, YO; Write RO into BASEPRI register MSR

Write RO into PRIMASK register PRIMASK, 70; BOOK SMSR

FAULTMASK, ro; write Ro into FAULTMASK register MSR

These registers cannot be set in the user access level.

Cortex-M3 Interrupt Mask Registers

A 1 1 bit register, when it is set, it allows NMI and hard fault exception; all other interrupts and exceptions PRIMASK are masked The default value is 0, which means that no masking

A1 bit register, when it is set, it allows only the NMI, and all interrupts and fault handling exceptions are FAULTMASK 565K and 1886 disabled. The default value is 0, which means that no marking

majs spressing for A register of upto 8 bits where it defines masking priority level. when it is set, it disables all interrupts BASEPRI of the same or lower level (larger priority value). sae), the sumbol Higher priority interrupts can still be allowed. The default value is as set to 0, the masking function is disabled.

# The Control Register

- It is a 2 bit register and is used to define the privilege level and the SP selection.

CONTROL [1] bit- is always 0 in handles made and however in thread or base level, it can be either 0 or 1.

It is writable only when the cone is in thread mode and privileged

- In the wer state or handler mode, writing to this bit not allowed.

→ Another way to change it is through to changing bit 2 of the LR when in exception return.

enters the user state, the only way to switch back to privileged is to trigger an interrupt and change this in the exception handler.

To access the control negister, in assembly - the MRS TO, CONTROL; Read CONTROL register into Ro.

MSR CONTROL, rO; Write RO into CONTROL register.

Cortex-M3 CONTROL REGISTER.

Bit

tiples to accers

CONTROL[1]

no principal and policies ou

aisteau (like MSR, except

CONTROL [0]

Function

Stack status:

1 = Alternate stack is used (PSP)

0 = Default stack (MSP) is used

If In thread or base level, the alternate stack is PSP. No alternate stack in handler mode.

Processor is in handler mode, when the

bit is 0. 0 = Privileged in thread mode.

1 = Wer state in thread mode.

It in handler mode (not thread mode), the processor operates in privileged mode.

## OPERATION MODE

The Cortex-M3 processor supports two modes and two privilege levels.

Operation Modes and Privilege Levels in Cortex-M3.

| thread made and                                           | Privileged                      | Useg                       |

|-----------------------------------------------------------|---------------------------------|----------------------------|

| When running an exception handler                         | Handler mode<br>(CONTROL [1] 0) | (not allowed)              |

| When not ownning an exception handler (e.g. main program) | Thread mode  (CONTROL [O] 0)    | Thread mode (CONTROL[0] 1) |

CONTROL[1] can be either 0 or 1.

-> When the processor is running in thread mode, it can be in either the privileged or user level, but handlers can only be in the privileged level.

- when the processor exits reset, it is in thread mode, with

privileged access rights.

In the user level (thread mode), access to the system control space (3CS) - a part of the memory region for configuration registers and debugging components - is blocked blocked.

Instructions that access special registery (like MSR, except

when accessing APSR) cannot be used access

→ When a programming is running, at user level tries to access SCS or special registers, a fault exception will occur.

If in handler mode (not thread mode),

-> Software in a privileged access level can switch the program into the wer access level using the control register.

when an exception takes place, the processor will always switch to a privileged state and return to the previous state when exiting the exception handler.

- A user program Cannot change back to the privileged state directly

by writing to the control register.

It has go to go through an a exception handler that programs the control register to switch the processor back into privileged access level when returning to thread mode.

Switching of Operation Mode by Programming the Control Registers or by Exceptions.

The support of both levels provides a more secure level & robust architecture. Ex- when a user program goes wrong due to NVIC, it will not be able to corrupt control registers. MPU avoids the user from accessing memory regions used by privileged processes and blocks user

In Simple applications, there is no need to separate the privileged and wer access levels. There is no be need to use user access level Enoneed

to program the Control register.

The user application stack is can be separated from the Kernel Stack memory to avoid crashing a system due to stack operation errors in user program.

Acc. to diagram, User program running in thread mode uses PSP, & the exception handless use the MSP. The switching of SPs is automatic

upon entering or leaving the exception handlers.

when an exception takes place.

-> When control register bit 0 is 1 (thread running wer application), both processor mode and access level change the when an exception

takes place.

is programmable only in the privileged level. For a userlevel program to switch to privileged state, it has to raise an Ex- Supervisor call [SVC], and write to CONTROL[0] within the handler.

# DEBUGGING SUPPORT -

-> Cortex-M3 processor includes a no. of debugging features such as program execution controls including halting and stepping, instruction break points, data watchpoints, registers and memory accesses, profiling and traces.

> Debugging hardware in Cortex M3 processor is based on Core sight

architecture.

- It does not have a JTAG interface like Traditional ARM processor instead DAP (Debug Access Port) is a debug interface module is decoupled from the core and a bus interface at core level.

- External debuggers can access control registers to debug hardware as well as System memory. When the processor is running.

- Debug Port, device controls the DAP bus interface and it is available as SW-DP (Social wire - JTAG). It supports traditional JTAG protocol as Serial wire protocol.

→ JTAG DP module from ARM cone sight product family can also be

- Chip manufacturers can use / choose attach one of these Debug port module to provide the debug interface.

- It also includes -ETM (Embedded Trace Macrocell) allows instruction trace and traced information is output through &TPIU (Trace Port Interface Unit) and the debug host (PC) can collect the executed instruction information via external trace capturing

hardware.

Events - In Cortex-M3 processor, a no. of events can be used to trigger beby debug actions.

-> tebug events can be breakpoints, watch points, fault conditions.

or external debugging request ilp signals.

-> When a debug event takes place, the Cortex M3 processor can either halt mode (or) execute the debug monitor exception handlen.

-Data watch point function is provided by a Data Watch Point and Trace (DWT) in Cortex M3 processon

- It can be used to stop the processor (or trigger the debug exception routine) or to generate data trace information.

- to when data trace is used, traced data can be output via the TPIU. Multiple trace devices can share one single trace port (TPIU).

- -) It allows also provides a Flash Patch and Break point (FPB) unit which can perform a simple break point function (or) remap an instruction access from Flash to a different location in SRAM. Hard remain miles and the second second

- TTM (Instrumentation Trace Macrocell) provides a new way for developers to output data to a debugger by writing data to register memory.

- Debugger can collect the data via trace interface interface and display or process them.

It is easy to use and faster than JTAG output.

- -> The Debugging components can be controlled by DAP interface bus (or) Program running on the Processor core.

- -> All Prace information is accessible from the TPIU.

Eventi- - In Cortex-M3 processor, a no. of eventi can be used

- Jebus a events can be break points, weath points, foult conditions

> When a debug event take place, the Costex M3 procussor

là trigger betos debug detions. I a

or external debugging respect is signals.

### EXCEPTIONS AND INTERRUPTS

- → The Cortex-M3 supports a no. of exceptions, including a fixed no. of System exceptions and a no. of Interrupts Commonly called

- -> The no. of interrupt inputs on a Cortex-M3 microcontrolles depends on the individual design.

- The typical no. of interrupt inputs is 16 or 32 bit.

It is generated by peripherals, except System Tick Timer also connected to interrupt input signals.

There is also a NMI (non maskable interrupt) input signal which depends on the design of the micro controller on system-on-chip (500).

- NMI could be connected to a Watch dog timer or a voltage-monitor--ing block that warns the processor when voltage drops below a certain level.

NMI can be activated at any time, even right after the core exit

-> A no. of the system exceptions are fault-handling exceptions that can be triggered by various error conditions.

-> NVIC also provides a no. of fault status registers so that error handlers can determine the cause of the exceptions.

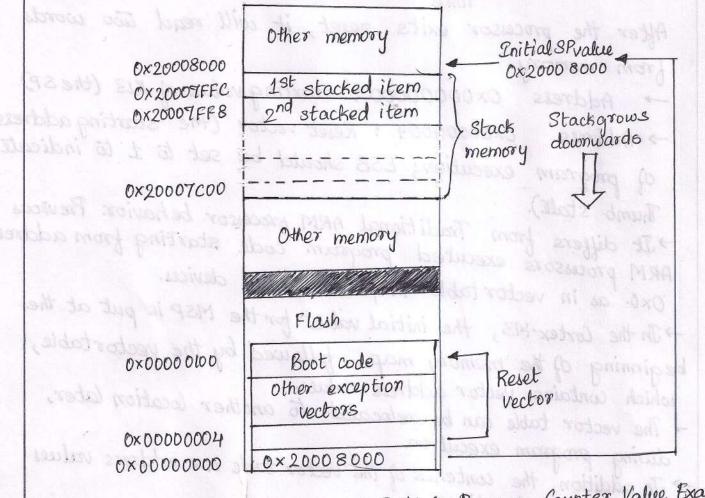

### VECTOR TABLES

-) When an exception event takes place on the Cortex-143 and is accepted by the Processor core, the corresponding exception handler is executed.

> Exception handler address is identified by Vector Table mechanism.

The Vector table is an array of word data inside the system memory, each representing the starting address of one exception type.

-> The Vector table is relocatable and the relocation is controlled by

a relocation register in the NVIC.

- After reset, Relocation control register is reset to 0. Vector table is located in address 0x00 after reset (exception type 1), the address of reset vector is I times of 4 (each word is 4 bytes), and NMI (type 2) is located at 0x04. 0x000004 and NMI(type2) is located in 2×4= 0×00 000 8.

- The address 0x00000000 is used to store the starting value for the MSP.

- The LSB of each exception vector indicates whether the exception is to be executed in the Thumb state.

- Fortex-M3 supports only Thumb instructions, the LSB of all the exceptions vectors should be set to 1.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Exception Types in Cortex M3                          |                                                                   |                                                                                                                                              |                                                                                                                                                         |                                                                                                                                                                   |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Exception                                             | Exception Type                                                    | Priority                                                                                                                                     | Function.                                                                                                                                               | of the expected for the                                                                                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 2 3                                                 | Reset<br>NMI<br>Hard fault                                        | -3(Highest)<br>-2<br>-1                                                                                                                      | All classes of fault handler of it is currently exception making                                                                                        | cannot be activated because disabled orman ted by                                                                                                                 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4<br>5<br>6<br>7-10<br>11<br>12<br>13<br>14           | Mem Manage Bus fault Chage fault  SVC Debugmonitor PendSV SYSTICK | Settable Settable Settable Settable Settable Settable Settable                                                                               | Memory manage<br>Error response rec<br>Usage fault;<br>Reserved<br>Supervisor call<br>Debug monitor<br>Reserved<br>Pendable request<br>System tick time | ment from the bus system reived from the bus system  I via SVC instruction  for system service                                                                    |  |

| The same of the same of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16-255                                                | IRB<br>able Definition                                            | Settable<br>after Rese                                                                                                                       | 1RQ input #0-2                                                                                                                                          | 284                                                                                                                                                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Exception To 18 - 255 17 16 15 14 13 12 11 7-10 6 5 4 | pe side sala<br>na side sala<br>na side sala<br>na side sala      | Address Q<br>0×48 - 0×<br>0×44<br>0×40<br>0×30<br>0×36<br>0×36<br>0×30<br>0×20<br>0×10 - 0×2<br>0×18<br>0×14<br>0×10<br>0×00<br>0×00<br>0×00 | gset 3FF                                                                                                                                                | Exception Vector  IRQ #2-239  IRQ #1  IRQ #0  SYSTICK  Pend SV  Reserved  Debug monitor  SVC  Reserved  Usage fault  Bus fault  Mem Manage fault  Hard fault  NMI |  |

| A STATE OF THE PARTY OF THE PAR | 2 0                                                   | gpe2) is locali                                                   | 0×04<br>0×0C                                                                                                                                 | A DOGODKO A                                                                                                                                             | Reset<br>Starting value of the MSP.                                                                                                                               |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                       |                                                                   |                                                                                                                                              | (0.0)                                                                                                                                                   |                                                                                                                                                                   |  |

STACK MEMORY OPERATIONS:-

-> In Cortex-M3 processor, besides normal software-controlled stack PUSH and POP, the stack PUSH and POP operations are also carried out automatically when entering or exiting an exception/interrupt handler.

Basic operations of the Stack.

- In general, stack operations are memory write or read operations with the address specified by SP.

- Data in registers is saved into stack memory by a PUSH operation and can be restored to registers later by a Popoperation.

-> The SP is adjusted automatically in PUSH and POP so that multiple data PUSH will not cause old stacked data to be erased.

The function of the stack is to store register contents in memory so that they can be nectored later, after a processing task is completed.

Stack Operation Basice: One Register in Each Stack Operation

; Ro = X, R1 = Y, R2 = Z

Subroutine

BL function1

Stack FOP and RETURN

function1 PUSH of Roy; store Ro to stack & adjust SP PUSH of RIG; store RI to stack & adjust SP PUSH of R24; store R2 to stack badjust SP ...; Executing task (Ro, RI, and R2 ; could be changed) of R24; restore R2 and SPre-adjusted POP

{RI}; restore R1 and SP re-adjusted {RO}; restore R0 and SP re-adjusted POP POP

LR; Return BX

; Back to main program

Executing task (Ro, RI and

; RO= X, RI=Y, R2=Z

-> For each store (PUSH), there must be a corresponding read (POP) and the ....; next instructions address of the Popoperation should match that of the PUSH operation.

-> When PUSH/POP instructions are used, the SP is incremented/ decremented automatically.

```

-> When program control returns to the main program, the RO-R2

contents are the same as before.

Notice the order of PUSH and POP: The POP order must be the

neverse of PUSH.

Stack Operation Basics: Multiple Register Stack operation.

Main program

subroutine

; RO =X, RI=Y, R2=Z

BL function1

> function1

PUSH {RO-R2}; store RO, RI, R2 to stack

...; Executing task (RO, RI and RZ

; could be changed)

PUSH and POP so that mu

POP (RO-R26; restore RO, RI, R2

BX LR 3 Return

; Back to main program

; Ro=X, R1=Y, R2=Z

···; next instructions

- These operations can be simplified, thanks to with PUSH and

POP instructions allowing multiple load and store.

- In this case, the ordering of a register POP is automatically

reversed by the Processor.

Stack Operation Basics: Combining Stack POP and RETURN

Main program

Subsoutine

; Ro = X, R1 = Y, R2 = Z

function 1

BL function1

[RO-R2, LR]; Save registers

PUSH

; including link register

; Executing task (RO, RI and R2

recibre so and space as included

; could be changed)

{RO-R2, PC}; Restore registers and

POP

; Back to main program

; Ro = X, RI = Y, R2=Z

...; next instructions

```

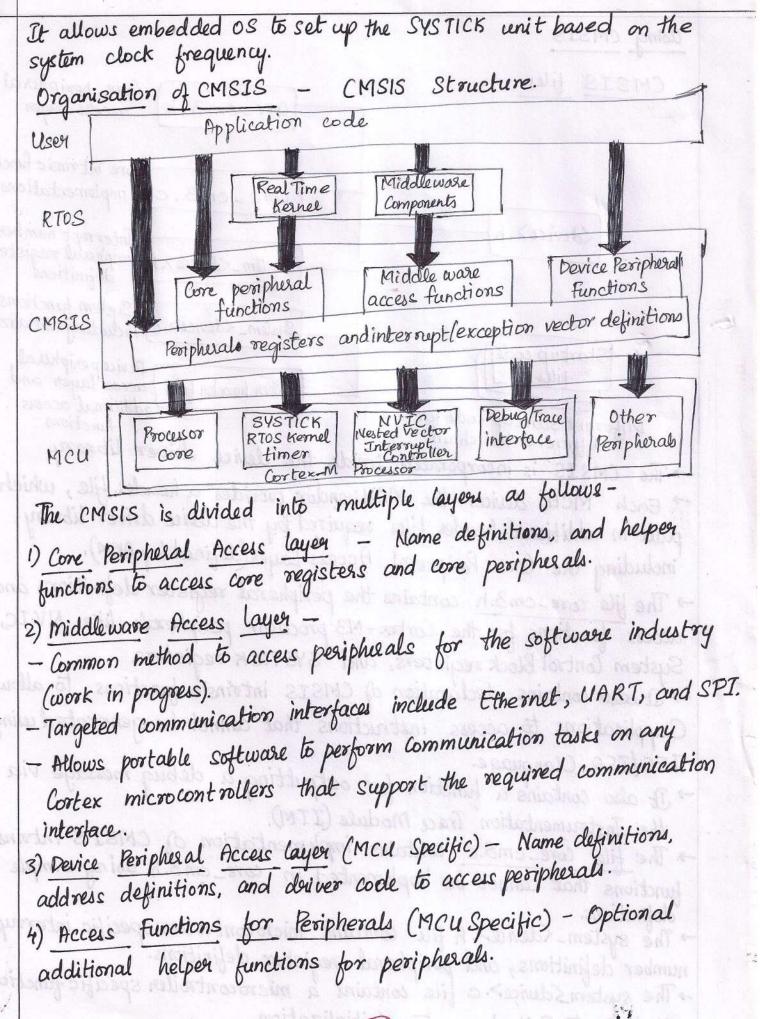

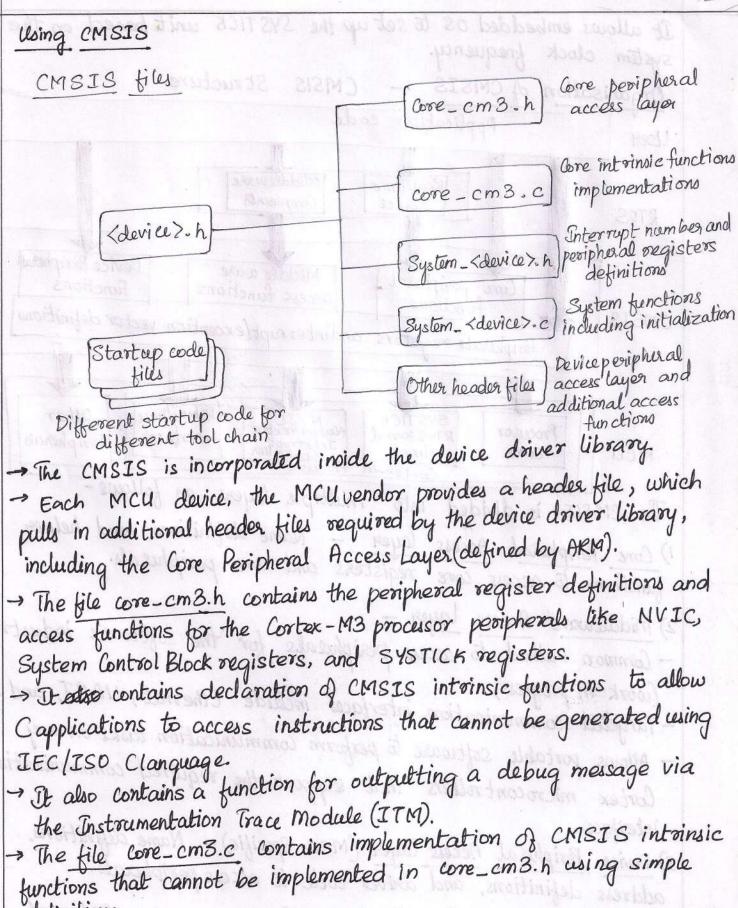

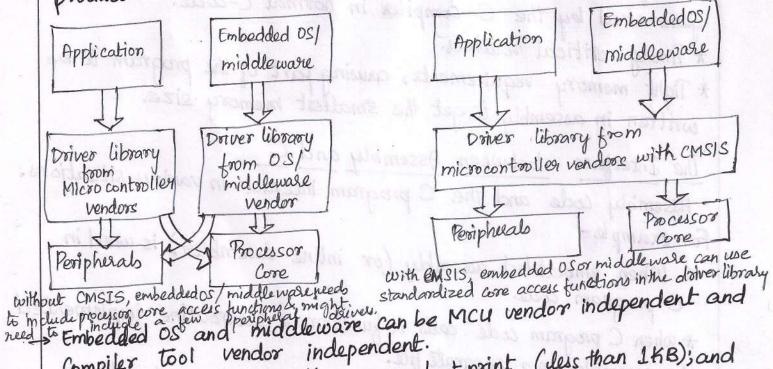

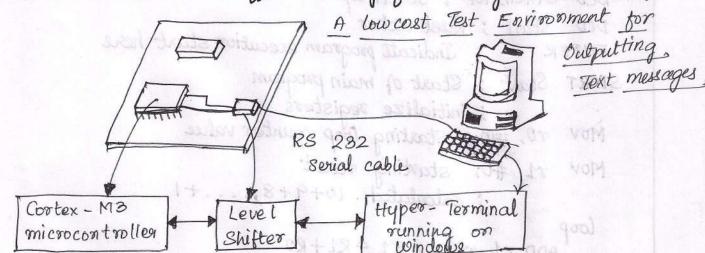

→ It combines RETURN with a Popoperation. It is done by pushing the LR to the stack and popping it back PC at the end of the subroutine.